AMD Zen 7 "Florence": Leak deutet auf Epyc-CPU mit 288 Cores und starke Effizienzsteigerung für Laptops

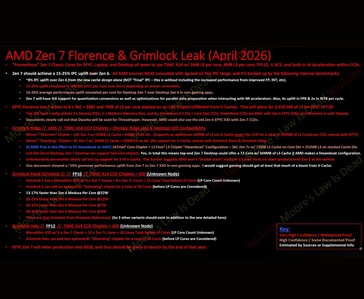

AMDs Server-Plattform der nächsten Generation könnte auch die Anzahl an Cores im Mainstream-Segment in Bereiche treiben, die vor nur wenigen Jahren noch undenkbar gewesen wären. Davon könnten möglicherweise auch Nutzer von Workstations und High-End-Desktops profitieren, da dort ähnliche Konfigurationen zum Einsatz kommen könnten. Laut einer Reihe von Folien, die der bekannte Hardware-Leaker Moore's Law Is Dead auf YouTube geteilt hat, setzt AMDs Zen 7 Epyc-Flaggschiff mit dem Codenamen Florence auf zwei "Dwarka"-I/O-Dies und zwei "Mathura"-Speicher-Dies. Beide Namen gehen auf antike indische Städte mit großer historischer und spiritueller Bedeutung zurück. Kombiniert werden sie mit bis zu acht Steamboat-CCDs mit jeweils 36 Cores, was 288 Cores pro Sockel entspricht.

Jeder Steamboat-CCD kombiniert einen Zen-7-Core-Die im A14-Verfahren von TSMC mit einem separaten L3-Cache auf N4P, der nicht wie beim aktuellen 3D V-Cache obenauf sitzt, sondern darunter gestapelt wird. Den Folien zufolge stehen 7MB L3-Cache pro Kern, eine PCIe 6 + CXL 3.2-Schnittstelle, eine xGMI4-80G-Link-Geschwindigkeit und eine TDP von bis zu 600 Watt im Raum.

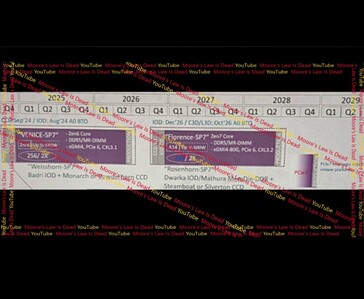

Sowohl der Dwarka-I/O-Die als auch der Mathura-Speicher-Die sollen im N3C-Verfahren von TSMC gefertigt werden. Eine der Slides zeigt ein für Oktober 2026 angesetztes A0-Tape-out, die Produktion ist demnach für Mitte 2028 vorgesehen, der Marktstart könnte gegen Ende desselben Jahres erfolgen. Ein separater Roadmap-Eintrag deutet zudem auf eine PCIe Gen 7-Plattform hin, die um 2029 erscheinen könnte, möglicherweise als Refresh in der Mitte des Produktzyklus auf einem neuen Sockel.

Käufer aktueller AMD-Plattformen müssen womöglich keinen Sockelwechsel einplanen, um vom nächsten großen Architektursprung zu profitieren. Besonders Notebook-Nutzer könnten zu den größten Gewinnern zählen. Aus den geleakten Dokumenten geht nämlich hervor, dass Zen-7-CCDs abwärtskompatibel zu I/O-Dies der vorherigen Generation mit den Codenamen Kedar und Weisshorn sein sollen. Silverton-CCDs sollen wiederum mit Badri-, Kedar-, Puri- und Dwarka-IODs in SP7- und SP8-Packages zusammenarbeiten. Unterstützt werden dabei 2, 4, 6 oder 8 CCDs pro Sockel. Die Unterstützung von Threadripper und HEDT über den Dwarka-IOD wird ausdrücklich erwähnt.

Eine separate Leistungstabelle für die auf Verbraucher ausgerichteten Silverton- und Silverking-Chipsätze nennt Leistungszuwächse pro Kern von 16 bis 20 Prozent bei Server-Workloads unter 9 Watt sowie 30 bis 36 Prozent in Client-APU-Szenarien mit 3 Watt pro Kern. Das deutet besonders bei dünnen und leichten Notebooks auf deutliche Effizienzgewinne hin.

Der YouTuber vermutet, dass die ähnliche Breite des 36-Kern-Steamboat-CCDs im Vergleich zum 16-Kern-Silverton es AMD theoretisch erlauben könnte, zwei Steamboat-CCDs auf AM5 unterzubringen, was in einem Desktop-Chip mit 72 Kernen resultieren würde. Eine geleakte Slide bestätigt ein solches Produkt allerdings nicht. Der Leaker selbst geht davon aus, dass ein derartiger Chip eher für Embedded-Kunden als für den DIY-Markt gedacht wäre.

Das unten verlinkte Video liefert einen detaillierten Blick auf die geleakten Informationen zu AMD Zen 7.